腦肌電多設備集成系統是一種融合腦電信號、肌電信號以及多種生理參數的高精度生物信號采集與分析平臺。在系統集成中,接口硬件設計起著關鍵作用,它確保各類設備之間的信號傳輸穩定、高效且無干擾。接口硬件設計不僅影響系統的整體性能,還直接關系到數據采集的準確性和實時性。

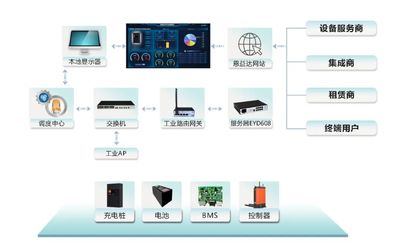

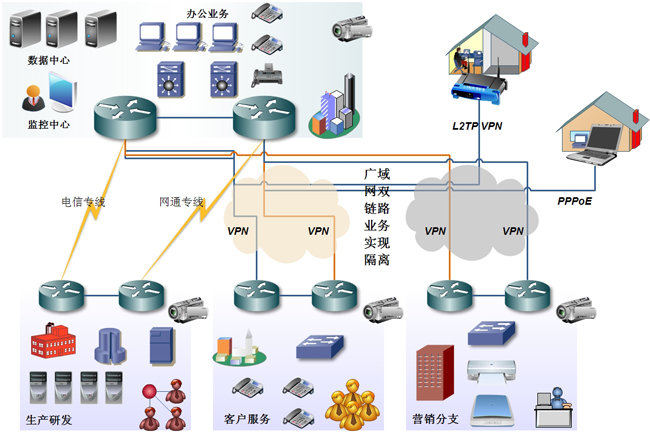

接口硬件設計需要滿足多設備兼容性。腦電設備和肌電設備通常采用不同的信號接口標準,如USB、藍牙、SPI或I2C。設計時應選擇通用且高速的接口協議,例如USB 3.0或以太網,以支持多通道數據同步傳輸。硬件接口應具備可擴展性,允許連接額外的傳感器或執行器,適應未來系統升級需求。

信號調理與轉換是接口硬件設計的核心。腦電和肌電信號屬于微弱生物電信號,容易受到環境噪聲干擾。因此,設計中需集成前置放大器、濾波電路和模數轉換器(ADC)。前置放大器用于提高信號幅度,濾波電路(如帶通濾波器)去除高頻噪聲和低頻漂移,而高精度ADC(例如24位)確保信號數字化過程中的保真度。接地和屏蔽措施必不可少,以最小化電磁干擾。

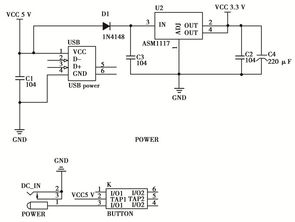

電源管理模塊是接口硬件的重要組成部分。多設備集成系統往往需要為不同設備提供穩定的電源,設計時應考慮功耗優化和隔離技術。例如,采用線性穩壓器或開關電源為模擬和數字部分分別供電,避免交叉干擾。加入過壓和過流保護電路,提升系統的安全性和可靠性。

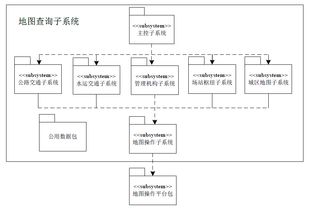

在通信協議方面,接口硬件需實現數據同步與實時傳輸。通過主控單元(如FPGA或微控制器)協調各設備,使用時間戳或觸發信號確保腦電和肌電數據的時間對齊。硬件接口應支持標準通信協議(如TCP/IP或自定義串行協議),便于與上位機軟件集成,實現數據可視化與分析。

系統集成測試是驗證接口硬件設計的關鍵步驟。通過模擬實際應用場景,檢查接口的帶寬、延遲和錯誤率。例如,使用信號發生器注入測試信號,評估系統的信噪比和動態范圍。集成過程中還需考慮機械接口設計,如連接器類型和布線方案,確保設備連接牢固且易于維護。

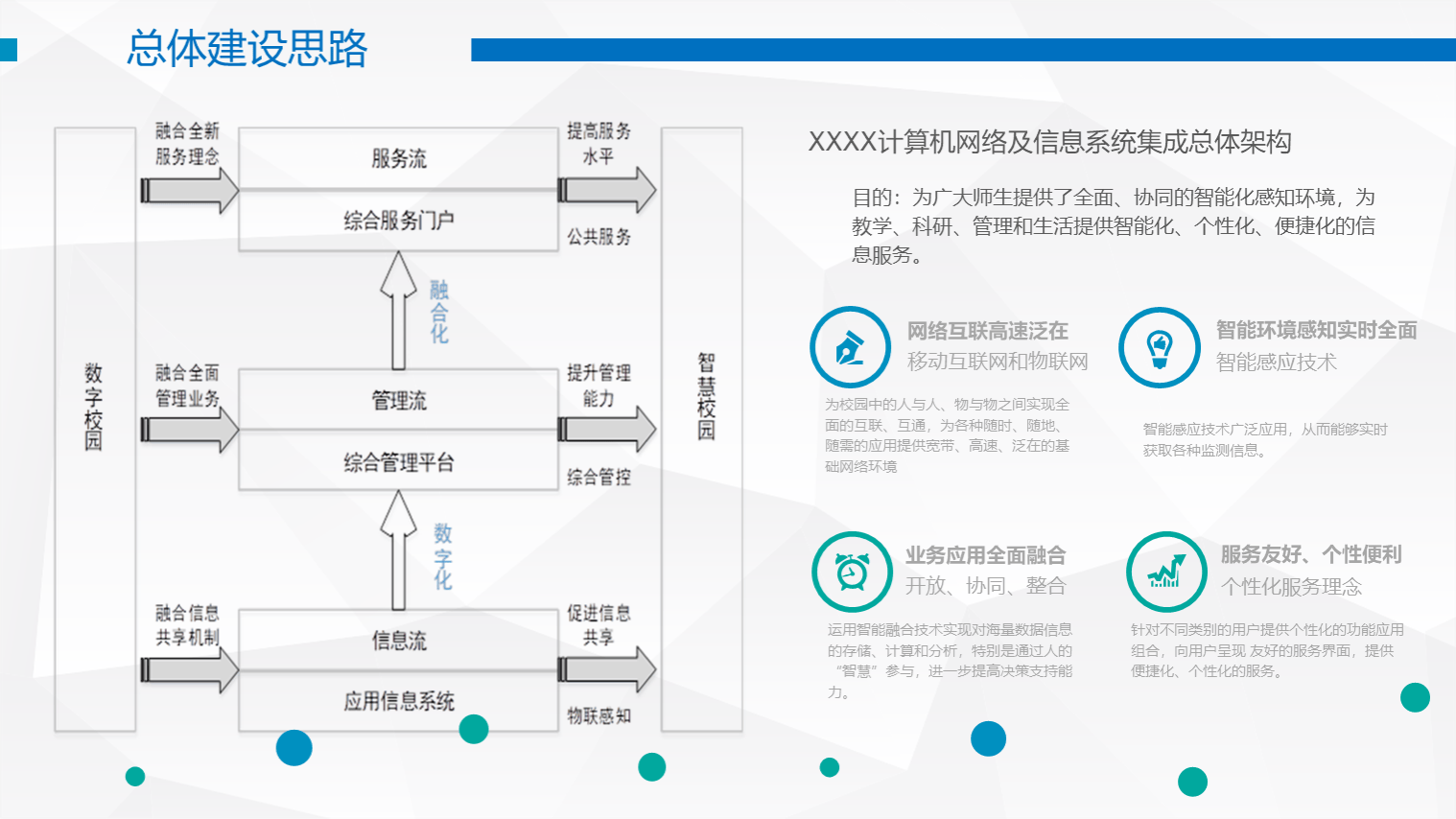

腦肌電多設備集成系統的接口硬件設計是一個多學科交叉的工程,涉及電子工程、信號處理和計算機科學。通過優化接口兼容性、信號調理、電源管理和通信協議,可以構建高效、可靠的集成系統,為神經科學研究和醫療應用提供強大支持。